Self-test Procedure

I2C and SPI firmware (FPGA configurations) for this Tap include test generators producing sustained test traffic at 400KHz and 24MHz respectively.

Test I2C signals are generated on D14 (SDA) and D15 (SCL).

Test SPI signals are generated on D12 (SS), D13 (MISO), D14 (MOSI), and D15 (SCLK).

To receive the test traffic, connect two or four wires as shown on the diagram below:

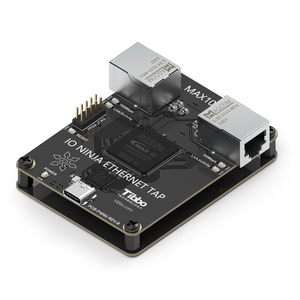

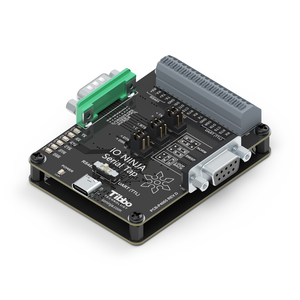

Key Features

- USB-powered, no additional external power necessary;

- Supplied with a

USB-C cable; - Based on Inter MAX10 FPGA;

- Incorporates an

I2C and SPI test sequence generator for self-testing the Tap; - Has 16 buffered IO lines

D0..D15 connected to a quick-release terminal block; - All buffers act as level shifters allowing the Tap to work with logical signals as high as 5V and as low as 1.8V;

- Eight LEDs onboard:

- Green

READY LED; - Two general-purpose green LEDs

M0 and M1 for mode and status indication; - Four yellow LEDs for indicating the state of IO lines

D0..D3 (sufficient for I2C and SPI); - Blue

POWER LED;

- Product functionality may be expanded in the future:

- Onboard FPGA is reconfigurable via the USB interface;

- Sixteen IO lines provide ample room to grow;

- It is envisioned that the product's abilities may be expanded to handle such protocols as...

Quad-SPI;SDIO;- Single-wire bus;

- ...and more!

Hardware Specifications

| Parameter | Value |

| USB: | USB 2.0, high-speed (480MHz), USB-C connector |

| Maximum I2C speed: | Up to 700KHz |

| Maximum SPI speed: | Up to 24MHz |

| Operating temperature: | 0 to +60 degrees C |

| Operating relative humidity: | 10% to 90% |

| Mechanical dimensions: | 82 x 74 x 30 mm |

This number depends on the host PC's performance and its workload. Captured data may be lost if PC's USB channel is unable to receive it in a timely manner. Our tests have shown that an average i7-based desktop PC that is not performing other time-critical tasks easily captures sustained SPI traffic with clock speeds up to 24MHz.

Documentation

Hardware Manual in PDF format